集成电路可靠性设计 从理论到实践的基石

在现代电子科技高度发达的今天,集成电路(IC)作为几乎所有电子设备的核心,其可靠性直接决定了终端产品的性能、寿命与安全。集成电路可靠性设计,已不再是传统设计流程中一个可选的后续优化环节,而是贯穿于从架构规划、电路实现到物理版图乃至封装测试的整个设计周期的核心指导思想。它旨在确保芯片在预期的寿命周期内,在规定的环境与工作条件下,能够持续、稳定、无误地执行其预定功能。

集成电路可靠性设计的挑战源于其本身日益增加的复杂性与物理极限的逼近。随着工艺节点不断微缩至纳米尺度,芯片面临着前所未有的可靠性威胁。这些威胁主要来自几个方面:

- 电迁移:在高电流密度下,金属互连线中的原子会因电子风的冲击而逐渐迁移,导致导线出现空洞(断路)或小丘(短路),最终引发功能失效。

- 热载流子注入:沟道中的高能载流子可能注入栅氧化层,造成器件阈值电压漂移和跨导退化,影响电路的长期稳定性。

- 负偏置温度不稳定性:对于PMOS晶体管,在负栅压和高温应力下,界面陷阱电荷会增加,导致阈值电压绝对值增大和驱动电流下降,严重影响数字电路的时序和模拟电路的精度。

- 时间依赖介电层击穿:栅氧化层在长期电场应力下会逐渐累积损伤,最终导致绝缘层突然击穿,造成器件永久性失效。

- 软错误:由宇宙射线或封装材料中的α粒子引发的随机性比特翻转,对存储器和高可靠性计算系统构成严重威胁。

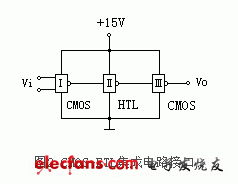

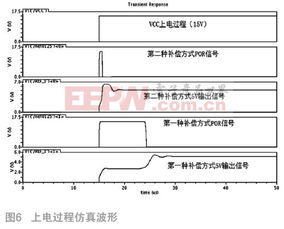

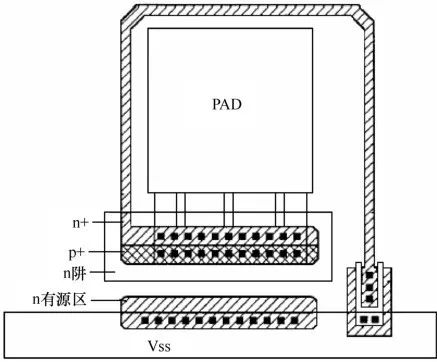

- 静电放电与闩锁效应:在制造、测试和使用过程中,静电可能瞬间损坏芯片;而寄生可控硅结构的意外触发(闩锁)则可能导致大电流烧毁电路。

面对这些挑战,可靠性设计必须采取系统性的方法,将可靠性考量“设计进去”,而非事后“检验出来”。其主要策略与技术包括:

- 设计裕度与降额使用:在设计时预留充足的性能和安全边界,例如使用更宽的导线以降低电流密度,使用低于额定值的电压或电流驱动器件,以减缓老化效应。

- 冗余设计:在关键路径或存储单元引入冗余。例如,三重模块冗余可以通过多数表决机制屏蔽单点故障;纠错码技术可以自动检测和纠正存储器中的软错误。

- 老化感知设计与时序分析:在设计阶段,通过模型预测电路在寿命周期内由于老化导致的性能退化(如速度变慢),并在静态时序分析中考虑这种退化,确保芯片在整个生命周期内都能满足时序要求。

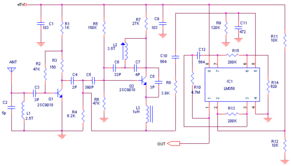

- 鲁棒性的电路与版图设计:采用对工艺波动和噪声不敏感的电路结构;在版图布局中遵循匹配、对称、保护环等设计规则,以抑制工艺偏差、噪声干扰和闩锁效应。

- 片上监测与自适应调整:集成温度传感器、老化监测电路等,实时感知芯片状态,并通过动态电压频率调整等技术,在性能和可靠性之间实现动态平衡。

- 系统级容错架构:在芯片架构层面设计故障检测、隔离与恢复机制,使系统在部分单元失效时仍能降级运行或安全关闭。

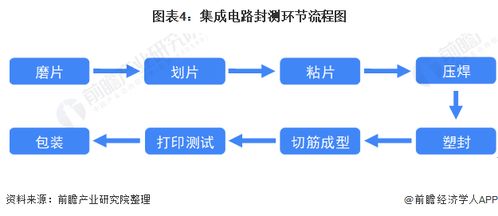

集成电路可靠性设计是一个多学科交叉的综合性工程领域,融合了器件物理、电路理论、计算机辅助设计和系统架构的知识。它要求设计工程师具备前瞻性的风险意识,在追求更高性能、更低功耗和更小面积的将可靠性作为一项根本的设计约束。随着集成电路在汽车电子、工业控制、航空航天和医疗设备等安全关键领域的广泛应用,可靠性设计的重要性将愈发凸显,成为决定产品成败和市场信誉的关键技术支柱。

如若转载,请注明出处:http://www.wifi-camera-alarm.com/product/11.html

更新时间:2026-03-13 13:03:43